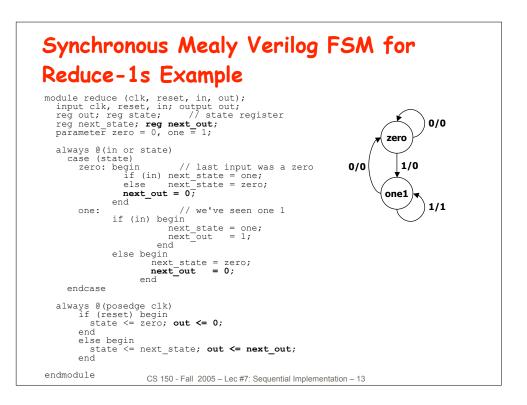

## Mealy Verilog FSM for Reduce-1s Example module reduce (clk, reset, in, out); input clk, reset, in; output out; reg out; reg state; // state register 0/0 reg next\_state; parameter zero = 0, one = 1; zero always @(in or state) 1/0 0/0 case (state) // last input was a zero zero: begin if (in) next\_state = one; else next\_state = zero; out = 0; one1) 1/1 end one: // we've seen one 1 if (in) begin next\_state = one; = 1; out end else begin next\_state = zero; out = 0; end endcase always @(posedge clk) if (reset) state <= zero; else state <= next state;</pre> endmodule CS 150 - Fall 2005 - Lec #7: Sequential Implementation - 12

## Uniquely Encode States

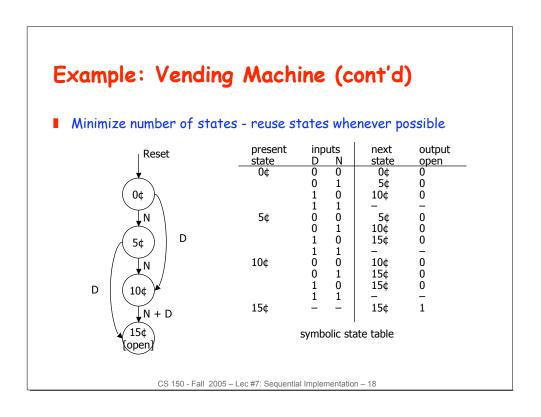

| present state<br>Q1 Q0 |             | inputs<br>D N |         |          | t state<br>D0 | output<br>open |  |

|------------------------|-------------|---------------|---------|----------|---------------|----------------|--|

| 0                      | 0           | 0<br>0        | 01      | 0        | 0             | 0              |  |

|                        |             | 1<br>1        | 0<br>1  | 1        | 0<br>—        | 0              |  |

| 0                      | 1           | 0<br>0        | 0<br>1  | 0<br>1   | 1<br>0        | 0              |  |

|                        |             | 1<br>1        | 0       | 1        | 1             | 0              |  |

| 1                      | 0           | 0             | 0       | 1        | 0<br>1        | 0              |  |

|                        |             | 1             | 0       | 1        | 1             | 0              |  |

| 1                      | 1           | -             | -       | - 1      | 1             | - 1            |  |

|                        |             |               |         | •        |               |                |  |

|                        |             |               |         |          |               |                |  |

|                        |             |               |         |          |               |                |  |

| CS 150 -               | Fall 2005 - | – Lec #       | #7: Sec | quential | Impleme       | ntation – 19   |  |

## One-hot Encoding

| present state | inputs |   | next state output |    |    |    |      |

|---------------|--------|---|-------------------|----|----|----|------|

| Q3 Q2 Q1 Q0   | D      | Ν | D3                | D2 | D1 | D0 | open |

| 0 0 0 1       | 0      | 0 | 0                 | 0  | 0  | 1  | 0    |

|               | 0      | 1 | 0                 | 0  | 1  | 0  | 0    |

|               | 1      | 0 | 0                 | 1  | 0  | 0  | 0    |

|               | 1      | 1 | -                 | -  | -  | -  | -    |

| 0 0 1 0       | 0      | 0 | 0                 | 0  | 1  | 0  | 0    |

|               | 0      | 1 | 0                 | 1  | 0  | 0  | 0    |

|               | 1      | 0 | 1                 | 0  | 0  | 0  | 0    |

|               | 1      | 1 | -                 | -  | -  | -  | -    |

| 0 1 0 0       | 0      | 0 | 0                 | 1  | 0  | 0  | 0    |

|               | 0      | 1 | 1                 | 0  | 0  | 0  | 0    |

|               | 1      | 0 | 1                 | 0  | 0  | 0  | 0    |

|               | 1      | 1 | -                 | -  | -  | -  | -    |

| 1 0 0 0       | -      | - | 1                 | 0  | 0  | 0  | 1    |

|               |        |   |                   |    |    |    |      |

|               |        |   |                   |    |    |    |      |

|               |        |   |                   |    |    |    |      |

|               |        |   |                   |    |    |    |      |

D0 = Q0 D' N' D1 = Q0 N + Q1 D' N' D2 = Q0 D + Q1 N + Q2 D' N' D3 = Q1 D + Q2 D + Q2 N + Q3 OPEN = Q3

CS 150 - Fall 2005 - Lec #7: Sequential Implementation - 21

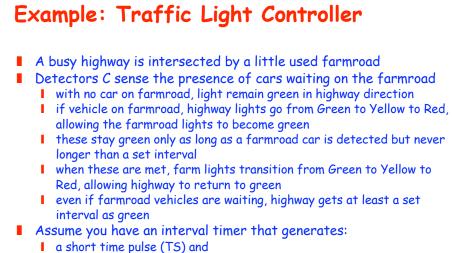

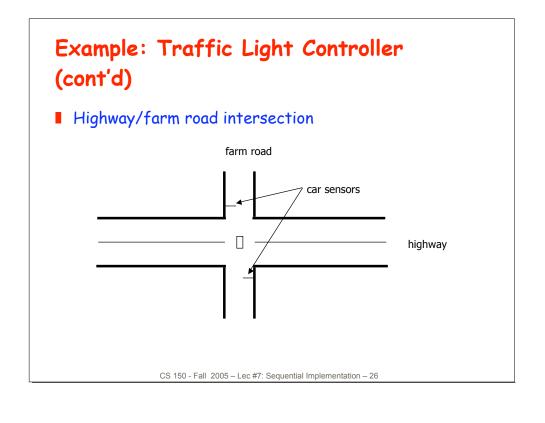

- a long time pulse (TL),

- in normania to a set (ET) sia

- in response to a set (ST) signal.

- TS is to be used for timing yellow lights and TL for green lights

CS 150 - Fall 2005 - Lec #7: Sequential Implementation - 25

## Sequential Logic Implementation Summary

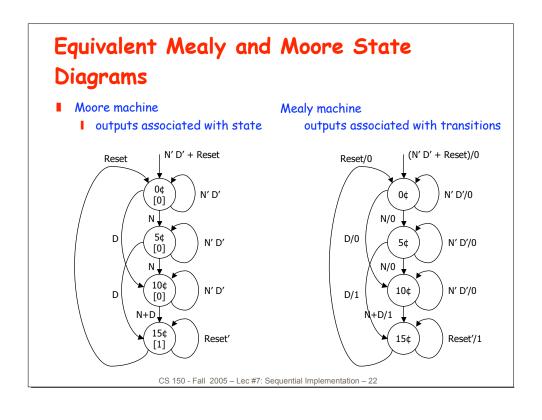

- Models for representing sequential circuits

- Abstraction of sequential elements

- Finite state machines and their state diagrams

- Inputs/outputs

- Mealy, Moore, and synchronous Mealy machines

- Finite state machine design procedure

- Verilog specification

- Deriving state diagram

- Deriving state transition table

- Determining next state and output functions

- I Implementing combinational logic

CS 150 - Fall 2005 - Lec #7: Sequential Implementation - 35